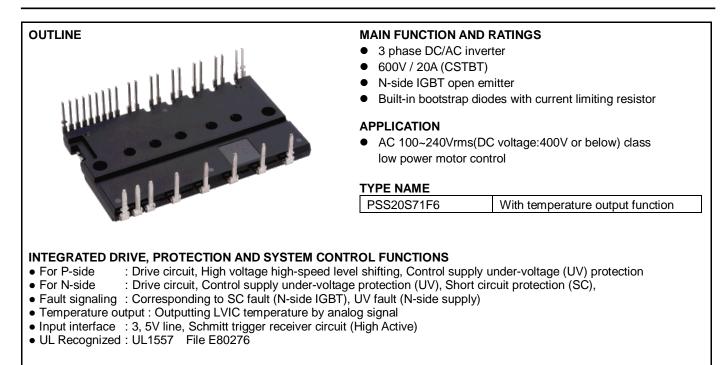

#### **INTERNAL CIRCUIT**

## **MAXIMUM RATINGS** ( $T_j = 25^{\circ}C$ , unless otherwise noted)

**INVERTER PART**

| Symbol                 | Parameter                          | Condition                         |          | Ratings  | Unit |

|------------------------|------------------------------------|-----------------------------------|----------|----------|------|

| Vcc                    | Supply voltage                     | Applied between P-NU,NV,NW        |          | 450      | V    |

| V <sub>CC(surge)</sub> | Supply voltage (surge)             | Applied between P-NU,NV,NW        |          | 500      | V    |

| VCES                   | Collector-emitter voltage          |                                   |          | 600      | V    |

| ±lc                    | Each IGBT collector current        | T <sub>C</sub> = 25°C             | (Note 1) | 20       | Α    |

| ±Іср                   | Each IGBT collector current (peak) | $T_{C}$ = 25°C, less than 1ms     |          | 40       | Α    |

| Pc                     | Collector dissipation              | T <sub>c</sub> = 25°C, per 1 chip |          | 76.9     | W    |

| Tj                     | Junction temperature               |                                   |          | -20~+150 | °C   |

Note1: Pulse width and period are limited due to junction temperature.

#### **CONTROL (PROTECTION) PART**

| Symbol          | Parameter                     | Condition                                                                           | Ratings                  | Unit |

|-----------------|-------------------------------|-------------------------------------------------------------------------------------|--------------------------|------|

| VD              | Control supply voltage        | Applied between V <sub>P1</sub> -V <sub>NC</sub> , V <sub>N1</sub> -V <sub>NC</sub> | 20                       | V    |

| V <sub>DB</sub> | Control supply voltage        | Applied between VUFB-VUFS, VVFB-VVFS, VWFB-VWFS                                     | 20                       | V    |

| VIN             | Input voltage                 | Applied between UP, VP, WP-VPC, UN, VN, WN-VNC                                      | -0.5~V <sub>D</sub> +0.5 | V    |

| V <sub>FO</sub> | Fault output supply voltage   | Applied between Fo-VNC                                                              | -0.5~V <sub>D</sub> +0.5 | V    |

| I <sub>FO</sub> | Fault output current          | Sink current at Fo terminal                                                         | 1                        | mA   |

| Vsc             | Current sensing input voltage | Applied between CIN-V <sub>NC</sub>                                                 | -0.5~V <sub>D</sub> +0.5 | V    |

#### TOTAL SYSTEM

| Symbol                 | Parameter                                                                     | Condition Rating                                                                           |          | Unit |

|------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------|------|

| V <sub>CC</sub> (PROT) | Self protection supply voltage limit<br>(Short circuit protection capability) | $V_D$ = 13.5~16.5V, Inverter Part<br>T <sub>j</sub> = 125°C, non-repetitive, less than 2µs | 400      | V    |

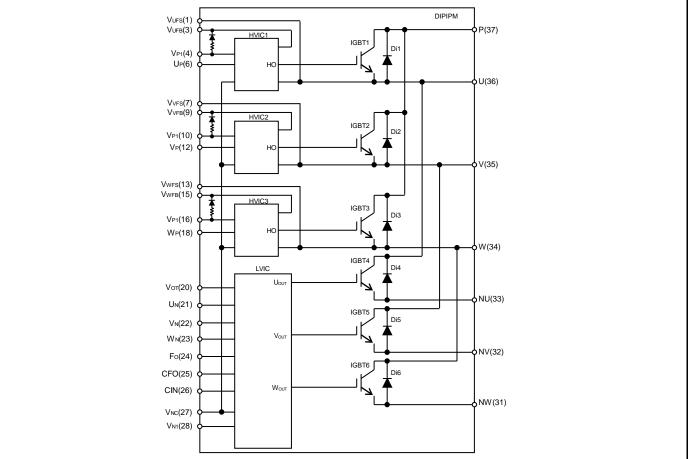

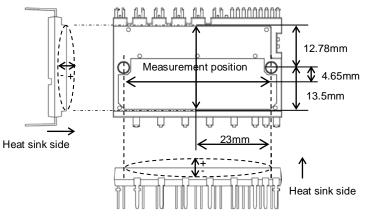

| Tc                     | Module case operation temperature                                             | Measurement point of Tc is provided in Fig.1                                               | -20~+100 | °C   |

| T <sub>stg</sub>       | Storage temperature                                                           |                                                                                            | -40~+125 | °C   |

| V <sub>iso</sub>       | Isolation voltage                                                             | 60Hz, Sinusoidal, AC 1min, between connected all pins and heat sink plate                  | 2500     | Vrms |

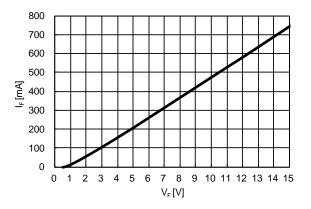

#### Fig. 1: Tc MEASUREMENT POINT

#### THERMAL RESISTANCE

| Symbol Parameter      |                          | Condition                           |      | Limits |      |      |  |

|-----------------------|--------------------------|-------------------------------------|------|--------|------|------|--|

| Symbol                | Parameter                | Condition                           | Min. | Тур.   | Max. | Unit |  |

| R <sub>th(j-c)Q</sub> | Junction to case thermal | Inverter IGBT part (per 1/6 module) | -    | -      | 1.3  | K/W  |  |

| R <sub>th(j-c)F</sub> | resistance (Note 2)      | Inverter FWDi part (per 1/6 module) |      | -      | 3.0  | K/W  |  |

|                       |                          |                                     |      |        |      |      |  |

Note 2: Grease with good thermal conductivity and long-term endurance should be applied evenly with about +100µm~+200µm on the contacting surface of DIPIPM and heat sink. The contacting thermal resistance between DIPIPM case and heat sink Rth(c-f) is determined by the thickness and the thermal conductivity of the applied grease. For reference, Rth(c-f) is about 0.3KW (per 1/6 module, grease thickness: 20µm, thermal conductivity: 1.0W/m•k).

#### ELECTRICAL CHARACTERISTICS (Tj = 25°C, unless otherwise noted) **INVERTER PART**

| Oursels al           | Descenden                    |                                                                      |                                                                      |      | Limits |      |      |  |

|----------------------|------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|------|--------|------|------|--|

| Symbol               | Parameter                    | Cond                                                                 | Condition                                                            |      | Тур.   | Max. | Unit |  |

| V                    | Collector-emitter saturation | VD=VDB = 15V. VIN= 5V                                                | I <sub>C</sub> = 20A, T <sub>j</sub> = 25°C                          | -    | 1.40   | 1.90 | v    |  |

| V <sub>CE(sat)</sub> | voltage                      | $v_{D}=v_{DB}=15v, v_{IN}=5v$                                        | Ic= 20A, Tj= 125°C                                                   | -    | 1.50   | 2.00 | v    |  |

| V <sub>EC</sub>      | FW Di forward voltage        | V <sub>IN</sub> = 0V, -I <sub>C</sub> = 20A                          | V <sub>IN</sub> = 0V, -I <sub>C</sub> = 20A                          |      |        | 2.00 | V    |  |

| t <sub>on</sub>      |                              |                                                                      |                                                                      | 0.95 | 1.55   | 2.15 | μs   |  |

| t <sub>C(on)</sub>   |                              | $V_{CC}$ = 300V, $V_{D}$ = $V_{DB}$ = 15V                            | -                                                                    | 0.50 | 0.80   | μs   |      |  |

| t <sub>off</sub>     | Switching times              | I <sub>C</sub> = 20A, T <sub>j</sub> = 125°C, V <sub>IN</sub> = 0↔5\ | I <sub>C</sub> = 20A, T <sub>j</sub> = 125°C, V <sub>IN</sub> = 0↔5V |      | 1.75   | 2.35 | μs   |  |

| t <sub>C(off)</sub>  |                              | Inductive Load (upper-lower a                                        | rm)                                                                  | -    | 0.40   | 0.60 | μs   |  |

| t <sub>rr</sub>      |                              |                                                                      |                                                                      | -    | 0.30   | -    | μs   |  |

| 1                    | Collector-emitter cut-off    | VCE=VCES                                                             | T <sub>j</sub> = 25°C                                                | -    | -      | 1    | m۸   |  |

| ICES                 | current                      | t VCE=VCES                                                           |                                                                      | -    | -      | 10   | mA   |  |

## CONTROL (PROTECTION) PART

| Symbol               | Parameter                              | Condition                                          |                                                           | Limits |      |      | Unit |

|----------------------|----------------------------------------|----------------------------------------------------|-----------------------------------------------------------|--------|------|------|------|

|                      |                                        | Colla                                              | 11011                                                     | Min.   | Тур. | Max. | Unit |

| 1                    |                                        | Tatal of $V_{D}=15V, V_{IN}=0V$                    |                                                           | -      | -    | 6.00 |      |

| ID                   |                                        | Total of $V_{P1}$ - $V_{NC}$ , $V_{N1}$ - $V_{NC}$ | V <sub>D</sub> =15V, V <sub>IN</sub> =5V                  | -      | -    | 6.00 | mA   |

|                      | Circuit current                        | Each part of VUFB- VUFS,                           | V <sub>D</sub> =V <sub>DB</sub> =15V, V <sub>IN</sub> =0V | -      | -    | 0.55 | mA   |

| DB                   |                                        | VVFB- VVFS, VWFB- VWFS                             | V <sub>D</sub> =V <sub>DB</sub> =15V, V <sub>IN</sub> =5V | -      | -    | 0.55 |      |

| V <sub>SC(ref)</sub> | Short circuit trip level               | V <sub>D</sub> = 15V                               | (Note 3)                                                  | 0.45   | 0.48 | 0.51 | V    |

| UV <sub>DBt</sub>    | P-side Control supply                  |                                                    | Trip level                                                | 10.0   | -    | 12.0 | V    |

| $UV_{DBr}$           | under-voltage protection(UV)           | Ti≤125°C                                           | Reset level                                               | 10.5   | -    | 12.5 | V    |

| UV <sub>Dt</sub>     | N-side Control supply                  | 1j=125 C                                           | Trip level                                                | 10.3   | -    | 12.5 | V    |

| UV <sub>Dr</sub>     | under-voltage protection(UV)           |                                                    | Reset level                                               | 10.8   | -    | 13.0 | V    |

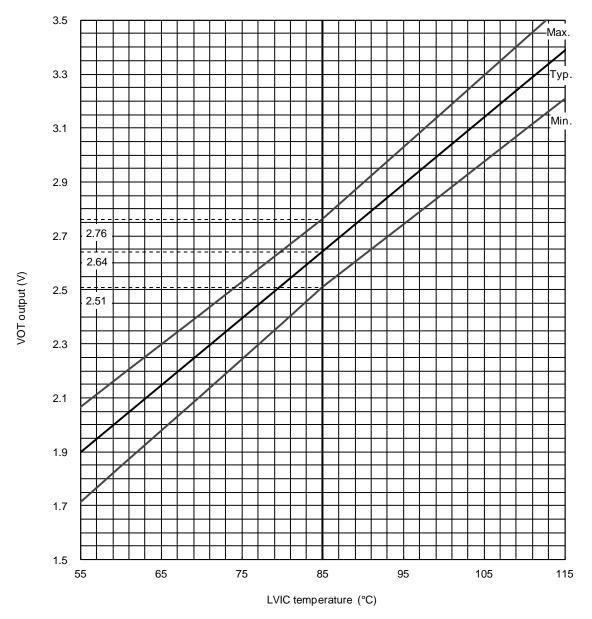

| Vot                  | Temperature Output                     | Pull down R=5kΩ (Note 4)                           | LVIC Temperature=85°C                                     | 2.51   | 2.64 | 2.76 | V    |

| VFOH                 |                                        | Vsc = 0V, Fo terminal pulled up                    | o to 5V by 10kΩ                                           | 4.9    | -    | -    | V    |

| VFOL                 | Fault output voltage                   | $V_{SC} = 1V$ , $I_{FO} = 1mA$                     |                                                           | -      | -    | 0.95 | V    |

| t <sub>FO</sub>      | Fault output pulse width               | C <sub>FO</sub> =22nF                              | (Note 5)                                                  | 1.6    | 2.4  | -    | ms   |

| I <sub>IN</sub>      | Input current                          | $V_{IN} = 5V$                                      |                                                           | 0.70   | 1.00 | 1.50 | mA   |

| V <sub>th(on)</sub>  | ON threshold voltage                   |                                                    |                                                           | -      | 2.10 | 2.60 |      |

| V <sub>th(off)</sub> | OFF threshold voltage                  | Applied between UP, VP, WP, UN, VN, WN-VNC         |                                                           | 0.80   | 1.30 | -    | v    |

| $V_{\text{th(hys)}}$ | ON/OFF threshold<br>hysteresis voltage |                                                    |                                                           | 0.35   | 0.80 | -    |      |

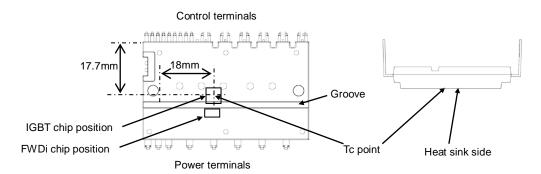

| V <sub>F</sub>       | Bootstrap Di forward voltage           | IF=10mA including voltage drop b                   | 0.5                                                       | 0.9    | 1.3  | V    |      |

| R                    | Built-in limiting resistance           | Included in bootstrap Di                           |                                                           | 16     | 20   | 24   | Ω    |

Note 3 : SC protection works only for N-side IGBT. Please select the external shunt resistance such that the SC trip-level is less than 2.0 times of the current rating. 4 : DIPIPM don't shutdown IGBTs and output fault signal automatically when temperature rises excessively. When temperature exceeds the protective level that user defined, controller (MCU) should stop the DIPIPM. Temperature of LVIC vs. VOT output characteristics is described in Fig. 3.

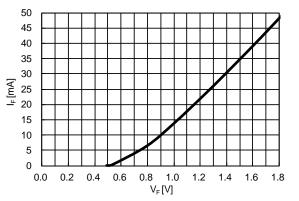

5 : Fault signal Fo outputs when SC or UV protection works. Fo pulse width is different for each protection modes. At SC failure, Fo pulse width is a fixed width which is specified by the capacitor connected to CFO terminal. (CFO=9.1 x 10<sup>-6</sup> x tFO [F]), but at UV failure, Fo outputs continuously until recovering from UV state. (But minimum Fo pulse width is the specified time by CFo.) 6 : The characteristics of bootstrap Di is described in Fig.2.

Fig. 2 Characteristics of bootstrap Di V<sub>F</sub>-I<sub>F</sub> curve (@Ta=25°C) including voltage drop by limiting resistor (Right chart is enlarged chart.)

Fig. 3 Temperature of LVIC vs. Vot output characteristics

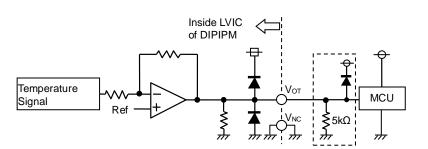

Fig. 4 Vor output circuit

- (1) It is recommended to insert  $5k\Omega$  (5.1 $k\Omega$  is recommended) pull down resistor for getting linear output characteristics at low temperature below room temperature. When the pull down resistor is inserted between V<sub>OT</sub> and V<sub>NC</sub>(control GND), the extra circuit current, which is calculated approximately by V<sub>OT</sub> output voltage divided by pull down resistance, flows as LVIC circuit current continuously. In the case of using V<sub>OT</sub> for detecting high temperature over room temperature only, it is unnecessary to insert the pull down resistor.

- (2) In the case of using V<sub>OT</sub> with low voltage controller like 3.3V MCU, V<sub>OT</sub> output might exceed control supply voltage 3.3V when temperature rises excessively. If system uses low voltage controller, it is recommended to insert a clamp Di between control supply of the controller and V<sub>OT</sub> output for preventing over voltage destruction.

- (3) In the case of not using  $V_{\text{OT}},$  leave  $V_{\text{OT}}$  output NC (No Connection).

Refer the application note for this product about the usage of  $V_{\text{OT}}$ .

# MECHANICAL CHARACTERISTICS AND RATINGS

| Parameter                 | Condition                    |                                      | Limits |      |      | Unit  |

|---------------------------|------------------------------|--------------------------------------|--------|------|------|-------|

| Parameter                 | Condition                    |                                      |        | Тур. | Max. | Unit  |

| Mounting torque           | Mounting screw : M3 (Note 7) | Recommended 0.78N·m                  | 0.59   | -    | 0.98 | N∙m   |

| Terminal pulling strength | Load 9.8N                    | JEITA-ED-4701                        | 10     | -    | -    | S     |

| Terminal bending strength | Load 4.9N, 90deg. bend       | Load 4.9N, 90deg. bend JEITA-ED-4701 |        | -    | -    | times |

| Weight                    |                              |                                      | -      | 21   | -    | g     |

| Heat-sink flatness        | (Note 8) -50 - 100           |                                      |        |      | μm   |       |

Note 7: Plain washers (ISO 7089~7094) are recommended.

Note 8: Measurement point of heat sink flatness

### **RECOMMENDED OPERATION CONDITIONS**

| Cumbal                       | Deremeter                       | Con                                                   | dition                                                                                    |                                 | Limits |      |      | Max. Unit |

|------------------------------|---------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------|--------|------|------|-----------|

| Symbol                       | Parameter                       | Con                                                   | Condition                                                                                 |                                 |        | Тур. | Max. |           |

| Vcc                          | Supply voltage                  | Applied between P-NU, NV                              | , NW                                                                                      |                                 | 0      | 300  | 400  | V         |

| VD                           | Control supply voltage          | Applied between VP1-VNC, V                            | / <sub>N1</sub> -V <sub>NC</sub>                                                          |                                 | 13.5   | 15.0 | 16.5 | V         |

| V <sub>DB</sub>              | Control supply voltage          | Applied between VUFB-VUFS                             | , V <sub>VFB</sub> -V <sub>VFS</sub> , V                                                  | wfb-Vwfs                        | 13.0   | 15.0 | 18.5 | V         |

| $\Delta V_D,  \Delta V_{DB}$ | Control supply variation        |                                                       |                                                                                           |                                 | -1     | -    | +1   | V/µs      |

| t <sub>dead</sub>            | Arm shoot-through blocking time | For each input signal                                 |                                                                                           |                                 | 1.5    | -    | -    | μs        |

| f <sub>PWM</sub>             | PWM input frequency             | T <sub>C</sub> ≤ 100°C, T <sub>j</sub> ≤ 125°C        |                                                                                           |                                 | -      | -    | 20   | kHz       |

| 1                            |                                 |                                                       |                                                                                           | f <sub>PWM</sub> = 5kHz         | -      | -    | 14.0 | Armo      |

| lo                           | Allowable r.m.s. current        | $T_c \le 100^{\circ}C, T_j \le 125^{\circ}C$          | Sinusoidal PWM<br>$T_c \le 100^{\circ}C, T_j \le 125^{\circ}C$ (Note9) $f_{PWM} = 15 kHz$ |                                 | -      | -    | 13.0 | Arms      |

| PWIN(on)                     |                                 |                                                       |                                                                                           | (Note 10)                       | 0.7    | -    | -    |           |

|                              | 1                               | 200V≤V <sub>CC</sub> ≤350V,                           | Below rate                                                                                | d current                       | 1.4    | -    | -    |           |

| PWIN(off)                    | Minimum input pulse width       |                                                       |                                                                                           | ated current<br>les of rated    | 2.5    | -    | -    | μs        |

|                              |                                 | N-line wiring inductance<br>less than 10nH (Note 11)  |                                                                                           | .7 times and<br>f rated current | 3.0    | -    | -    |           |

| V <sub>NC</sub>              | V <sub>NC</sub> variation       | Between V <sub>NC</sub> -NU, NV, NW (including surge) |                                                                                           |                                 | -5.0   | -    | +5.0 | V         |

| Tj                           | Junction temperature            |                                                       |                                                                                           |                                 | -20    | -    | +125 | °C        |

Note 9: Allowable r.m.s. current depends on the actual application conditions.

10: DIPIPM might not make response if the input signal pulse width is less than PWIN(on)

11: IPM might make delayed response or no response for the input signal with off pulse width less than PWIN(off). Please refer below about delayed response.

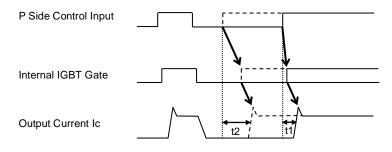

Delayed Response against Shorter Input Off Signal than PWIN(off) (P-side only)

Real line: off pulse width > PWIN(off); turn on time t1 Broken line: off pulse width < PWIN(off); turn on time t2 (t1:Normal switching time) Fig. 5 Timing Charts of The DIPIPM Protective Functions

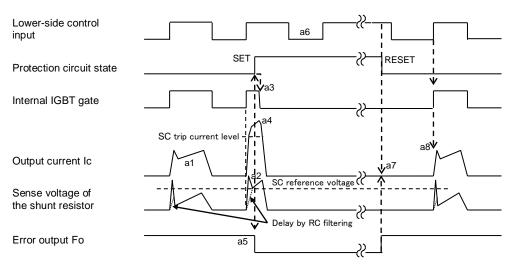

[A] Short-Circuit Protection (N-side only with the external shunt resistor and RC filter)

- a1. Normal operation: IGBT ON and outputs current.

- a2. Short circuit current detection (SC trigger)

- (It is recommended to set RC time constant 1.5~2.0µs so that IGBT shut down within 2.0µs when SC.)

- a3. All N-side IGBT's gates are hard interrupted.

- a4. All N-side IGBTs turn OFF.

- a5. F<sub>0</sub> outputs. The pulse width of the Fo signal is set by the external capacitor  $C_{\text{FO}}$ .

- a6. Input = "L": IGBT OFF

- a7. Fo finishes output, but IGBTs don't turn on until inputting next ON signal (L $\rightarrow$ H).

- (IGBT of each phase can return to normal state by inputting ON signal to each phase.) a8. Normal operation: IGBT ON and outputs current.

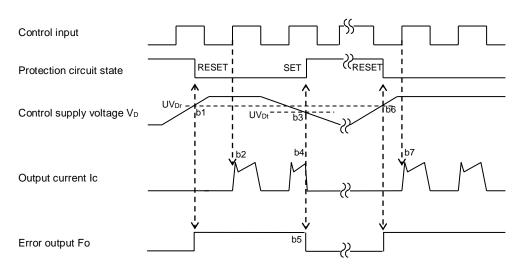

[B] Under-Voltage Protection (N-side, UV<sub>D</sub>)

- b1. Control supply voltage V<sub>D</sub> exceeds under voltage reset level (UV<sub>Dr</sub>), but IGBT turns ON by next ON signal (L $\rightarrow$ H). (IGBT of each phase can return to normal state by inputting ON signal to each phase.)

- b2. Normal operation: IGBT ON and outputs current.

- b3. V<sub>D</sub> level drops to under voltage trip level. (UV<sub>Dt</sub>).

- b4. All N-side IGBTs turn OFF in spite of control input condition.

- b5. Fo outputs for the period set by the capacitance C<sub>FO</sub>, but output is extended during V<sub>D</sub> keeps below UV<sub>Dr</sub>.

- b6.  $V_D$  level reaches  $UV_{Dr}$ .

- b7. Normal operation: IGBT ON and outputs current.

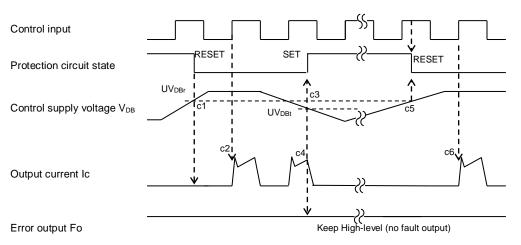

[C] Under-Voltage Protection (P-side, UV<sub>DB</sub>)

- c1. Control supply voltage V<sub>DB</sub> rises. After the voltage reaches under voltage reset level UV<sub>DBr</sub>, IGBT turns on by next ON signal (L→H).

- c2. Normal operation: IGBT ON and outputs current.

- c3.  $V_{DB}$  level drops to under voltage trip level (UV<sub>DBt</sub>).

- c4. IGBT of the correspond phase only turns OFF in spite of control input signal level, but there is no Fo signal output.

- c5.  $V_{DB}$  level reaches  $UV_{DBr}$ .

- c6. Normal operation: IGBT ON and outputs current.

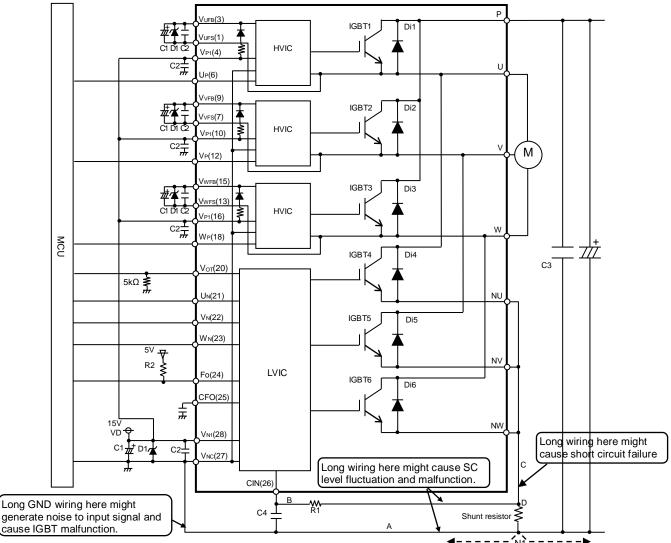

### Fig. 6 Example of Application Circuit

Control GND wiring N1 Power GND wiring

- (1) If control GND is connected with power GND by common broad pattern, it may cause malfunction by power GND fluctuation. It is recommended to connect control GND and power GND at only a point N1 (near the terminal of shunt resistor).

- (2) It is recommended to insert a Zener diode D1(24V/1W) between each pair of control supply terminals to prevent surge destruction.

(3) To prevent surge destruction, the wiring between the smoothing capacitor and the P, N1 terminals should be as short as possible. Generally a 0.1-0.22µF snubber capacitor C3 between the P-N1 terminals is recommended.

- (4) R1, C4 of RC filter for preventing protection circuit malfunction is recommended to select tight tolerance, temp-compensated type. The time constant R1C4 should be set so that SC current is shut down within 2μs. (1.5μs~2μs is recommended generally.) SC interrupting time might vary with the wiring pattern, so the enough evaluation on the real system is necessary.

- (5) To prevent malfunction, the wiring of A, B, C should be as short as possible.

- (6) The point D at which the wiring to CIN filter is divided should be near the terminal of shunt resistor. NU, NV, NW terminals should be connected at near NU, NV, NW terminals when it is used by one shunt operation. Low inductance SMD type with tight tolerance, temp-compensated type is recommended for shunt resistor.

- (7) All capacitors should be mounted as close to the terminals as possible. (C1: good temperature, frequency characteristic electrolytic type and C2:0.22µ-2µF, good temperature, frequency and DC bias characteristic ceramic type are recommended.)

- (8) Input logic is High-active. There is a 3.3kΩ(min.) pull-down resistor in the input circuit of IC. To prevent malfunction, the input wiring should be as short as possible. When using RC coupling, make the input signal level meet the turn-on and turn-off threshold voltage.

- (9) Fo output is open drain type. It should be pulled up to power supply of MCU (e.g. 5V,3.3V) by a resistor that makes I<sub>Fo</sub> up to 1mA. (I<sub>FO</sub> is estimated roughly by the formula of control power supply voltage divided by pull-up resistance. In the case of pulled up to 5V, 10kΩ (5kΩ or more) is recommended.) When using opto coupler, Fo also can be pulled up to 15V (control supply of DIPIPM) by the resistor.

- (10) Fo pulse width can be set by the capacitor connected to CFO terminal.  $C_{FO}(F) = 9.1 \times 10^{-6} \times t_{FO}$  (Required Fo pulse width).

- (11) If high frequency noise superimposed to the control supply line, IC malfunction might happen and cause DIPIPM erroneous operation. To avoid such problem, line ripple voltage should meet dV/dt ≤+/-1V/µs, Vripple≤2Vp-p.

- (12) For DIPIPM, it isn't recommended to drive same load by parallel connection with other phase IGBT or other DIPIPM.

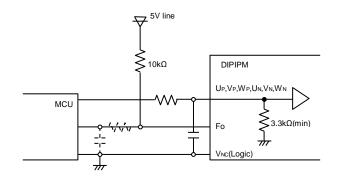

Fig. 7 MCU I/O Interface Circuit

Note)

Design for input RC filter depends on PWM control scheme used in the application and wiring impedance of the printed circuit board. DIPIPM input signal interface integrates a minimum  $3.3k\Omega$ pull-down resistor. Therefore, when inserting RC filter, it is necessary to satisfy turn-on threshold voltage requirement.

Fo output is open drain type. It should be pulled up to control power supply (e.g. 5V, 15V) with a resistor that makes Fo sink current I<sub>Fo</sub> 1mA or less. In the case of pulled up to 5V supply, 10k $\Omega$  (5k $\Omega$  or more) is recommended.

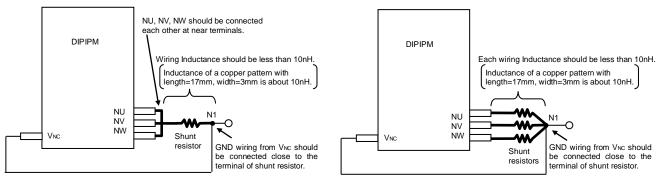

#### Fig. 8 Pattern Wiring Around the Shunt Resistor

Low inductance shunt resistor like surface mounted (SMD) type is recommended.

#### Fig. 9 Pattern Wiring Around the Shunt Resistor (for the case of open emitter)

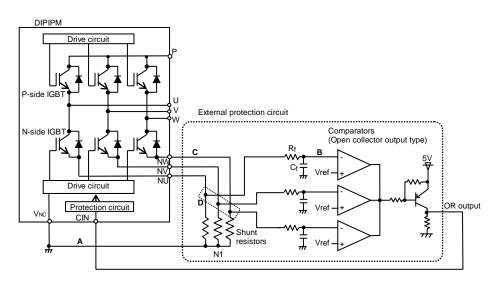

When DIPIPM is operated with three shunt resistors, voltage of each shunt resistor cannot be input to CIN terminal directly. In that case, it is necessary to use the external protection circuit as below.

(1) It is necessary to set the time constant  $R_i C_i$  of external comparator input so that IGBT stops within 2µs when short circuit occurs.

SC interrupting time might vary with the wiring pattern, comparator speed and so on.

(2) It is recommended for the threshold voltage Vref to set to the same rating of short circuit trip level (Vsc(ref): typ. 0.48V).

(3) Select the external shunt resistance so that SC trip-level is less than specified value (=2.0 times of rating current).

(4) To avoid malfunction, the wiring A, B, C should be as short as possible.

(5) The point D at which the wiring to comparator is divided should be close to the terminal of shunt resistor.

(6) OR output high level when protection works should be over 0.51V (=maximum Vsc(ref) rating).

(7) GND of Comparator, GND of Vref circuit and Cf should be not connected to power GND but to control GND wiring.

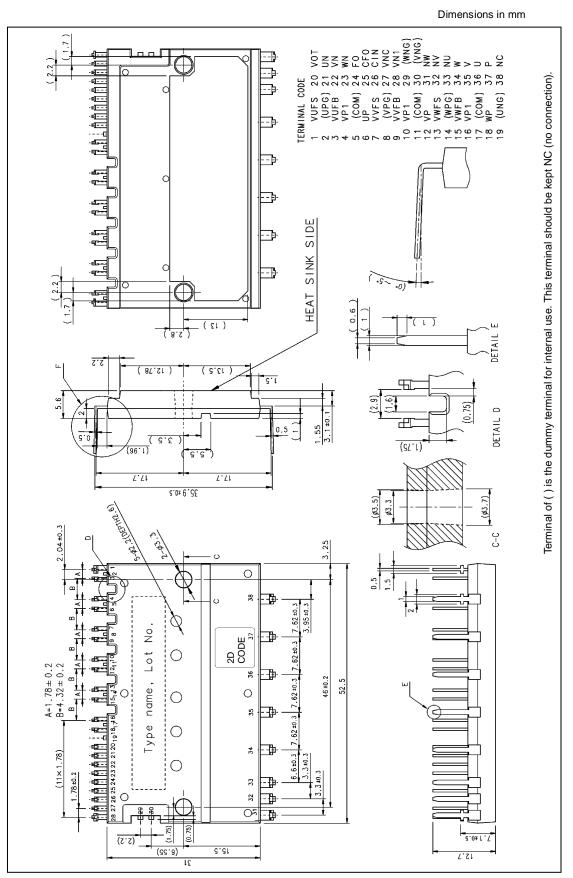

Fig. 10 Package Outlines

**Revision Record**

| Rev. | Date       | Page | Revised contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 15/10/2013 | -    | New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2    | 25/12/2013 | 5    | Revise misdescription (Condition of Terminal pulling strength and Terminal bending strength)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3    | 12/ 2/2014 | 1    | [INTERNAL CIRCUIT] Revise misdescription of terminal name(VUFS, VUFB, VVFS, VVFB, VV |

|      |            | 10   | Fig.10 Annotation is added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4    | 15/ 3/2014 | 2    | Add Note1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4    | 15/ 3/2014 | 3    | Revise misdescription of the condition of VoT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5    | 7/ 8/2018  | 5    | JEITA-ED-4701 was EIAJ-ED-4701                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5    | 17 8/2018  | 10   | Change phrase to 2D CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# Keep safety first in your circuit designs!

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

# Notes regarding these materials

- •These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- •Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- •All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.MitsubishiElectric.com/semiconductors/).

- •When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- •Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- •The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- •If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or re-export contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

•Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

© 2018 MITSUBISHI ELECTRIC CORPORATION. ALL RIGHTS RESERVED. DIPIPM and CSTBT are trademarks of MITSUBISHI ELECTRIC CORPORATION.